Morgan Stanley Just Reduced TSMC’s Value By $25B While Demonstrating A Complete Lack of Semiconductor Knowledge

Taiwanese Semiconductor Manufacturing Company, $TSM, is the world’s largest contract chip manufacturer. They have been the most valuable semiconductor company ever since they surpassed Intel and Samsung in valuation. The recipe for success has been simple. Pushing forward Moore’s law. They are building the worlds most advanced chips for clients, helping them achieve goals they need for their use cases and workloads. All the while, they are deadly efficient. TSMC is the key enabler powering the worlds biggest trends from smartphones, 5G, AI, Internet of Things, and any other buzzword you can think of.

Recently, Morgan Stanley analysts have downgraded the company’s stock in an 83-page report which caused it’s market cap to tumble by $25 billion. The main reason?

We think TSMC can barely maintain its 50% gross margin in a semi up-cycle – let alone in a down-cycle, as we expect in 2022

Morgan Stanley

TSMC has been extending their lead over competition such as Intel, Samsung, and GlobalFoundries. Their customers such as Apple, AMD, Nvidia, and Amazon are fully disrupting the industry and growing market share like mad. These firms are powered by leading edge silicon from TSMC. Why would their single enabler suddenly start having worse gross margins?

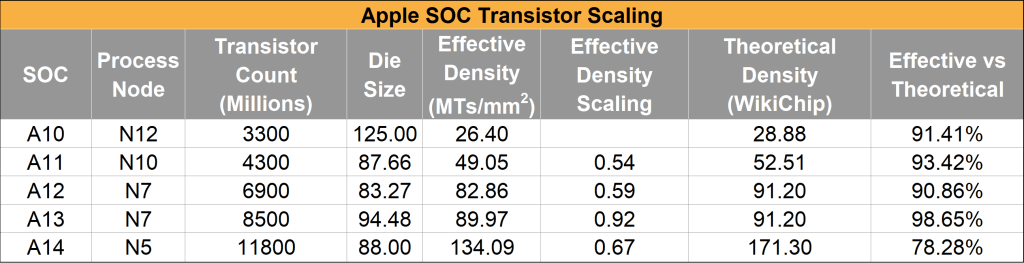

Morgan Stanley believes that because Moore’s law is slowing down, and transistor cost scaling has stopped, TSMC’s pricing pressure will diminish. Morgan Stanley justified this by including a laughable chart that showed transistor costs on 5nm being lower than 7nm. This in stark contrast to industry experts. Cost per transistor stalled with the introduction of FinFET nodes, 7nm completely plateaued, and with 5nm they are higher than ever before. Our readers can do the math, N7 wafers are ~$9,500 and N5 wafers are ~$16,000. Apple’s die size barely fell.

Based on this we can see costs per transistors have already begun to rise at the N5 node.

Strike 1 Morgan Stanley.

Despite transistor costs rising, Apple is happily spending more on their chip generation to generation. This is clearly apparent when looking at their phone chips. With the Mac transition to Apple silicon, this will trend continues. Intel gets kicked out, and all that volume moves to TSMC fabricated Apple silicon. Apple eats the margin that Intel used to have and provides many more transistors per chip in their client products. This delivers a better product with higher performance and battery life, which in turn drives and sales. The business case for shrinking with higher transistor costs is here.

This same philosophy applies to the other tech giants such as Amazon, Google, Microsoft, Facebook, etc. They have vertical integration ambitions and are on the path to designing their own silicon. They chase shrinks for the power efficiency boosts. For the performance increases. The chips they buy are not commodities whose sole factor is pricing.

The same philosophy for these giants also applies to merchant silicon. If we look around the industry, semiconductor costs as a portion of total bill of materials has continually risen. Silicon content is up despite transistor costs decreases having halted and reversed course over the last few few years ago. AMD is another perfect example of this phenomenon. In just a handful of years they have gone from the much cheaper Global Foundries 14nm and 12nm nodes to the much more expensive cost per transistor TSMC 7nm node and soon 5nm nodes. Furthermore, the amount of silicon they ship with each successive generation has increased. The cost to manufacture has increased despite heavy utilization of chiplets. This double whammy of more expensive process technologies and more silicon has resulted in…. AMD datacenter sales soaring and higher gross margins.

Using leading edge nodes gives you higher performance and reduces power use. Your chips command a higher premium and result in better TCO or experience for the end user. 5nm increased cost per transistor yet it has record tape outs planned by TSMC clients. Each tape out represents a design which utilizes the process. These tape out decisions were made well after they learned that the price per transistor increases.

The demand from TSMC clients is there, and that is with the 5nm node commanding incredibly high prices. Margins are not hurt, in fact they still have room to expand. There is only true 1 player in town for the leading edge. Qualcomm and Nvidia are trying to work with Samsung, who offers a much lower cost per transistor, but cost alone does not dictate design wins. They both still heavily utilize TSMC and are going to increase their utilization in the coming years. TSMC has pricing power.

Strike 2 Morgan Stanley.

We think the cycle peak could happen as early as in 4Q21 when foundry tightness starts to ease

Morgan Stanley

As an independent analyst I have been able to do channel checks that validate 2022 is still part of this super cycle. I shudder at the fact that 5 different analysts at Morgan Stanley could not pick up their phone and call people within the ecosystem. Leadtime’s for components are not 25 weeks. Many components are ranging from more than 30 weeks. Some are even backed up over a year. This is for existing orders. TSMC has already negotiated wafer supply for 2022 and are working on 2023 with major clients according to local Taiwanese media.

Hey Morgan Stanley, maybe that’s why they are spending $30B each year on additional supply...

Now, you may scream that there are double orders in place, but many folks in the semiconductor ecosystem are playing this cycle smart. They are making non-refundable, non-cancellable orders. The semiconductor industry has learned through the numerous boom and bust cycles. They are scabbed, beat up, and cautious against oversupply. This applies to all fields of semi, whether its logic like TSMC’s main market, DRAM, NAND, or analog.

So no, Morgan Stanley, there is no possibility of foundry tightness easing in Q4 2021 given orders are already booked. There will be tightness for TSMC through the entirety of 2022.

Strike 3 Morgan Stanley

This is where I would say “You’re out!”, but the report is 83 pages and still has a few hilarious complete misunderstandings that I want to point out.

5G migration is already halfway through

Morgan Stanley

Morgan Stanley likely looks at the number of phones sold with 5G and called it a day. About half of phones sold do have 5G. That does not mean that all 5G smartphone solutions are built equal. Many existing 5G sales will transition to higher performance modems, transceivers, and mmWave antennas over time. China is going to light up mmWave in 2022 or 2023. These all drive silicon up for TSMC despite having already made the switch to 5G.

Half of all networks have not made the switch to 5G either. China, USA, Japan, South Korea and Europe are not hallway through with 5G infrastructure build out despite having turned on 5G. Countries such as India have barley started and their mobile traffic per user is soaring incredibly fast. There is a long way to go on 5G demands for silicon, and it extends well beyond just smartphones and network infrastructure. Edge compute and IoT are "5G migrations" that are just getting started.

Strike 4 Morgan Stanley

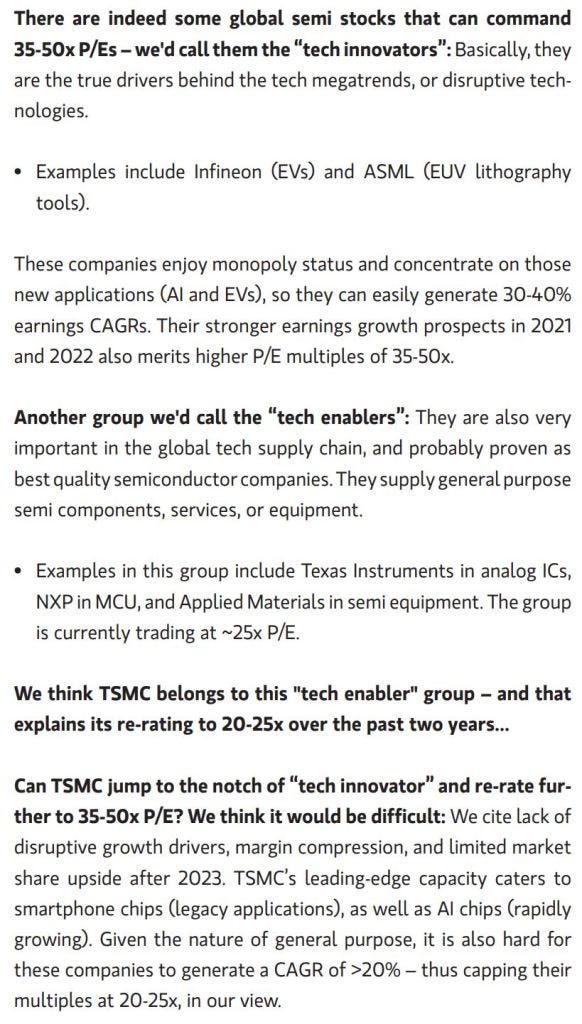

The imaged above is perhaps the most egregious part of the entire report. Morgan Stanley just called TSMC lower quality and lower innovation than Infineon. Infineon is a nice firm, they enable some interesting technology changes such as the electrification and coming smart grids. They absolutely do not belong in the “tech innovator” group. They are not leading electric vehicles semiconductors. They are not driving tech megatrends and they certainly are not introducing disruptive technologies. Their power related ICs are not massively complex, they do not command high gross margins. Infineon is a squarely a “tech enabler”.

TSMC is a “tech innovator.” Their technology is enabling entire ecosystems to change. They create chips with over 10 billion transistors in size of your nail. They are essentially building 10 billion on off switches that are perfectly arranged to make sand think. They are doing this for dozens of different companies at the same time who are targeting vastly different designs and use cases. They are offering high levels of customization.

We will try not to rant about why Applied Materials belongs in the “tech innovator” group because of their innovations with new materials or their position in other process steps and equipment for manufacturing semiconductors. It is likely that Morgan Stanley simply read a bit about EUV and decided that it was the only technology driving Moore’s law while ignoring the hundreds of other process steps involved.

Strike 5 Morgan Stanley

Advanced 3D packaging to dilute the value of monolithic scaling. The world is changing from monolithic integration (or conventional Moore's Law scaling) to multi-die and multi-chip systems, which is what AMD and Intel call "chiplets." That would dilute TSMC's value added in leading-edge foundry business.

Morgan Stanley

Morgan Stanley just dismissed 3D packaging as hurting TSMC's lead on the leading edge. This makes absolutely no sense at all. 3D packaging is a front-end technology. One cannot simply order chiplets from a foundry and choose to use low margin outsourced test and assembly firms to package these chips together. 3D packaging is primarily a way of bringing more transistors closer together. 3D does not allow trailing edge content to replace leading edge. TSMC's 3D technology dubbed SoIC is only available on 7nm and more advanced process technologies. Furthermore, even in 2D chiplet technologies such as current AMD datacenter CPUs, leading edge content isn't skimped in favor of leading edge. They are additive.

AMD will be releasing the industries first 3D hybrid bonded CPUs alongside TSMC soon. Moving to 3D allows AMD for example to include more leading-edge silicon per product. This service increases TSMC’s lead and increases TSMC’s sales. The death of SRAM scaling is a major driving factor behind this decision to move to 3D. We wrote about some of the implications here, but to cut a long story short, the solution is much more leading edge silicon. 3D packaging complements leading edge and allows products to include more leading edge silicon content than ever before. A method for increasing the silicon content per product being written off as dilutive is just hilariously wrong.

Strike 6 Morgan Stanley

However, an innovation in system architecture can easily boost system/chip performance 50-100%, some with much lower costs. NVIDIA has been the slowest adopter of TSMC's leading-edge node, by upgrading its GPU architecture every year

Morgan Stanley

Nvidia is on a 2 year cycle for both gaming and datacenter GPUs. Morgan Stanley somehow could not even look at Nvidia’s history of products or their public roadmaps. Nvidia has adopted the most advanced node that TSMC offers for their datacenter product every release. They work closely with TSMC in the past to build the largest monolithic chip possible because their demands require it. They work closely with TSMC to stack this massive GPU on top of a silicon interposer and package HBM memory. They are working with TSMC on 5nm GPUs with more advanced packaging for datacenter next year which will increase leading edge silicon beyond the monolithic realm limits.

Nvidia charges $10k for their datacenter GPUs, and they fly off the shelves. If Samsung or Intel were manufacturing, these would not be as powerful or efficient. Nvidia's architecture prowess allows the portability of software and ease of use. It enables the new use cases for GPUs. Most power usage on GPUs is still burned on data movement and computation. Nvidia GPUs are enabled by TSMC’s prowess in leading edge silicon and advanced packaging.

Strike 7 Morgan Stanley

We are just on page 19 folks, and for our sanity, we will stop here for this note. Don’t worry, the rest of the report does not disappoint and is a consistent level of poor quality “analysis”. How do 5 Morgan Stanley semiconductor analysts write an 83 page report and make such glaringly obvious mistakes? They did not even try to Google some of the most basic facts. They did not pick up the phone and run these things by people who work in the industry.

“Hanlon’s Razer” says they are just incompetent, but I must go with “Occam’s Razer” here. They may be somewhat incompetent, but they also wanted to go against the tide of the market and claim something bombastic because it is II Voting Season. They certainly achieved what they wanted. Most institutional investors invested in TSMC read this piece of crap report. Some of them relied on this and sold the stock causing the valuation of TSMC to fall by $25 billion. Now these Morgan Stanley analysts are fresh on their mind during II Voting Season.

This article was originally published on SemiAnalysis on June 23rd 2021.

Clients and employees of SemiAnalysis may hold positions in companies referenced in this article.

Powerful analysis! Thank you very much for sharing Patel.

I was totally shocked when I read the MS report. They are basically asking investors to trust some sell-side analysis instead of leaders from TSMC....

loved this piece... i gave up on that report after page 5.. I admire your ability to last till page 19...